TiferKing的学习笔记

这里记录了TiferKing的学习历程

-

记录一次boot sector的编写

前段时间学了一点点关于操作系统的东西,跟着一本分析Linux 0.11 内核代码的书学习的,刚开始的时候,书中…

-

第三章:C++中的C

在使用C++编写程序的时候,我们会发现其中很多地方所使用的语句与C语言十分相似,其实从其命名可以看出来,C++…

-

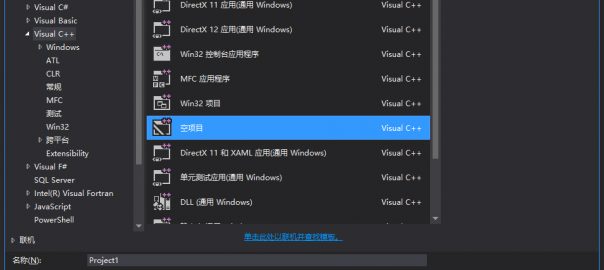

VS2015 搭建汇编编译环境 编译汇编

在编辑汇编程序的时候,可能一般情况下很多人会使用到像记事本或者notepad++这类工具,因为可以进行语法高亮…

-

第二章:对象的创建与使用 (2) (利用C++标准库创建对象)

在我们进行编程的时候,并不需要每次都从零开始构建一个程序,往往我们可以使用一些由其他人或者先前的工程师进行精心…

-

第二章:对象的创建与使用 (1) (基础知识与基本语法)

可以说,从这里开始算是C++的起步了,在接触对象之前,需要了解如何在一段代码当中创建以及使用一个对象。而在这之…

-

第一章:对象导言

最近听了别人的安利,对Think in C++这本书产生了一定的兴趣,刚开始读的时候,觉得甚是晦涩,因为它满篇…

-

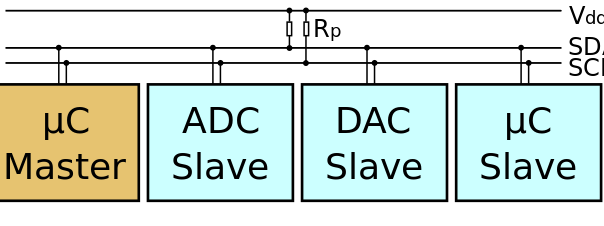

IIC总线协议小记 附函数库

最近参加了TI公司赞助的电子大赛,学到了很多的东西,想着写出来分享一下,于是也就有了这篇博文。 首先来谈谈II…

-

TI杯电赛小记

感觉很久很久都没有打开自己的博客了,不知不觉已经一年过去了,仿佛这一年过得好快,所有这一年来的经历记忆,还都历…

-

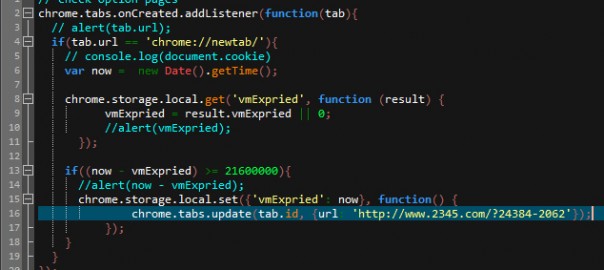

从根本解决 chrome 浏览器在 打开新标签页 的时候弹出 2345 主页

最近快要过年了,过年嘛,事情比较多,所以好长时间没有更新,主要也是没什么材料更新。(瞎说什么大实话)不过无论如…

-

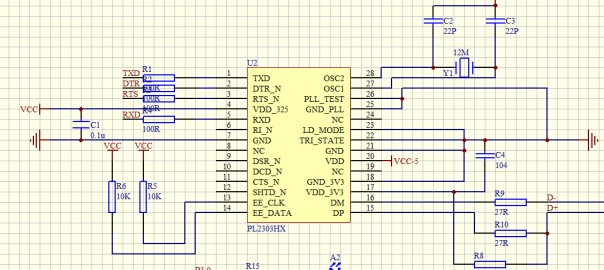

pl2303 转串口与 msp430 通信时遇到的问题

前一段时间在做一个小的系统,然后为了用起来方便,于是想着自己做一个usb转串口的bsl下载器。一个是因为手头正…

-

html前台使用js生成文件哈希(hash)

这次要认认真真的写一篇文章了,咳咳。 关于如何前台生成文件hash的文章。 之前在网上找了很多文章都没有特别详…

-

php 文件输出 文件头部有多余字符

最近用到了php对文件下载和上传的操作,上传的时候倒是没什么大的问题,但是在下载的时候,文件总是多一些奇奇怪怪…